特征

•14通道伽马校正

•2个VCOM输出

•片上OTP存储器

•10位分辨率

•轨对轨输出

•低电源电流:1mA/ch

•电源电压:8.5V至18V

•数字电源:2.0V至5.5V

•行业标准,双线接口:3.4MHz高速模式

•高ESD额定值:4kV HBM,1kV CDM,200V毫米

•提供演示板和软件

应用

•取代基于电阻的伽马解决方案

•TFT-LCD参考驱动程序

•动态伽马控制

说明

BUF16820是一个可编程基准电压发生器,设计用于TFT-LCD面板中的伽马校正。它提供14个可编程输出和两个VCOM通道,每个通道的分辨率为10位。它提供片上一次性可编程(OTP)存储器,允许用户在芯片上存储伽马电压。这样就不需要外部EEPROM。

这种可编程性取代了传统的、耗时的改变电阻值以优化各种伽马电压的过程,并允许设计者快速确定面板的正确伽马电压。也可以在不改变硬件电压的情况下轻松实现。

BUF16820采用了TI最新的小几何模拟CMOS工艺,这使得它成为全面生产的一个非常有竞争力的选择,而不仅仅是评估。

通过工业标准的两线串行接口对每个输出进行编程。与现有的可编程缓冲器不同,BUF16820提供了一种高速模式,允许时钟速度高达3.4MHz。

对于频道数较低或较高的设备,请联系您当地的销售或营销代表。

BUF16820在HTSSOP-32中提供PowerPAD软件包。规定温度范围为−40°C至+85°C。

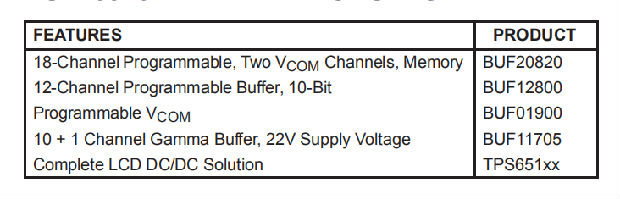

BUF16820相关产品

典型特征

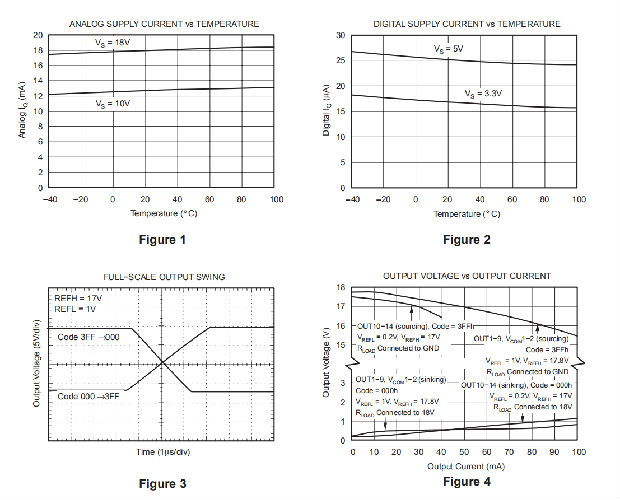

TA=+25°C,VS=18V,VSD=5V,VREFH=17V,VREFL=1V,RL=1.5kΩ接地,CL=200pF时,除非另有说明。

应用程序信息

BUF16820可编程基准电压允许快速方便地调整14个可编程参考输出和两个用于VCOM调整的通道,每个通道具有10位分辨率。它允许对伽马基准电压和VCOM电压进行非常简单、高效的调整。BUF16820是通过高速标准双线接口编程的。BUF16820为每个DAC通道提供了双寄存器结构,以简化动态伽马控制的实现。这种结构允许预加载寄存器数据和同时快速更新所有通道。

缓冲器1−9能够在正极供电轨200mV范围内摆动,在负极供电轨0.6V范围内摆动。负向轨10.0伏范围内的正缓冲器向轨10.0伏供电。

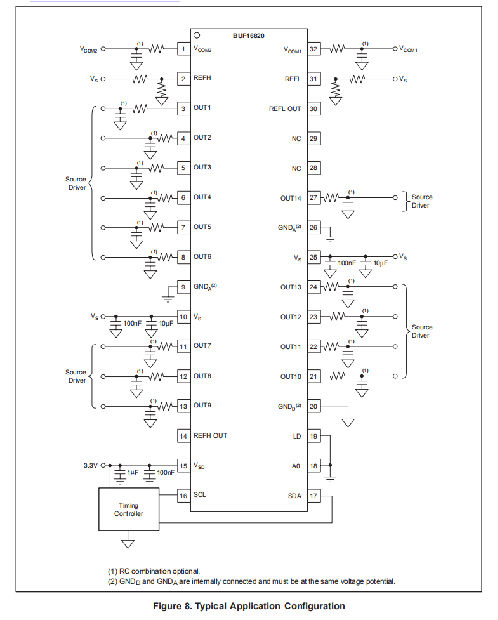

BUF16820可以使用8.5V到18V的模拟电源电压和2V到5.5V的数字电源供电。数字电源必须在模拟电源之前或同时使用,以避免过多的电流和功耗;如果长时间只连接模拟电源,可能会损坏设备。图7显示了电源定时要求。

图8显示了典型配置中的BUF16820。在这种配置中,BUF16820设备地址为74h。一旦在相应寄存器(LD=0)中接收到数据,每个数模转换器(DAC)的输出立即更新。对于最大动态范围,设置VREFH=VS−0.2V,VREFL=GND+0.2V。

双线总线概述

BUF16820通过工业标准双线接口进行通信,以从模式接收数据。本标准使用两线制开路漏极接口,支持单个总线上的多个设备。总线只驱动到逻辑低电平。发起通信的设备称为主设备,主设备控制的设备为奴隶们主机在时钟信号线(SCL)上生成串行时钟,控制总线访问,并生成启动和停止条件。

为了对特定设备进行寻址,当SCL处于高电平时,主机通过将数据信号线(SDA)从高逻辑电平拉到低逻辑电平来启动启动条件。总线上的所有从机都在从机地址字节中移位,最后一位表示是要进行读操作还是写操作。在第9个时钟脉冲期间,被寻址的从机通过产生一个应答并将SDA拉低来响应主机。

然后开始数据传输,发送8位数据,然后发送一个确认位。在数据传输过程中,当SCL较高时,SDA必须保持稳定。当SCL较高时,SDA的任何变化都将被解释为启动或停止条件。

一旦所有数据都被传输,主设备会生成一个停止条件,在SCL为高时,将SDA从低拉到高。

BUF16820只能作为从设备;因此,它从不驱动SCL。SCL引脚只是BUF16820的输入。表1和表2分别总结了BUF16820的地址和命令代码。

处理BUF16820

BUF16820的地址是111010x,其中x是A0引脚的状态。当A0引脚低时,设备将在地址74h(1110100)上确认。如果A0引脚高,设备将在地址75h(1110101)上确认。

其他有效地址可以通过简单的掩码更改来实现。请联系您的TI代表以获取信息。

数据速率

双线总线以三种速度模式之一运行:

*标准——允许时钟频率高达100kHz;

*快速——允许时钟频率高达400kHz;

*高速——允许时钟频率高达3.4MHz。

BUF16820完全兼容所有三种模式。在标准或快速模式下使用设备无需特殊操作,但必须激活高速(Hs)模式。要激活Hs模式,在启动条件后发送一个特殊地址字节00001xxx,SCL=400kHz;其中xxx是支持Hs的主机的唯一位,可以是任何值。这个字节称为Hs主代码。(请注意,这与正常地址字节不同,低位不表示读/写状态。)无论最后三位的值如何,BUF16820都将响应Hs命令。BUF16820将不确认该字节;通信协议禁止确认Hs主代码。收到主代码后,BUF16820将打开其Hs模式滤波器,并以高达3.4MHz的频率进行通信。通过生成无停止的重复启动,可以在不重新发送Hs模式字节的情况下启动附加的高速传输。BUF16820将在下一个停止条件下退出Hs模式。

一般呼叫重置和通电

BUF16820响应一般呼叫重置,即地址字节00h(0000 0000 0000),后跟数据字节06h(0000 0110)。BUF16820承认这两个字节。在接收到一般呼叫重置后,BUF16820会执行完全内部重置,就好像它已经断电然后再打开一样。它总是确认00h(0000 0000)的一般呼叫地址字节,但不确认除06h(0000 0110)以外的任何一般呼叫数据字节。

BUF16820通电后自动执行复位。作为重置的一部分,BUF16820配置为所有输出,以更改为已编程的OTP存储器值,或在OTP值未编程的情况下更改为0000。

当发送设备地址时,BUF16820将所有输出重置为OTP内存值(如果OTP值尚未编程,则重置为0000),然后发送一个有效的DAC地址,D7到D5位设置为“100”。如果这些位设置为'010',则只有在此最高有效字节和以下最低有效字节中寻址的DAC将被重置。

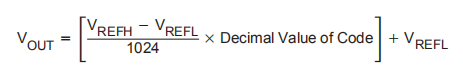

输出电压

缓冲器输出值由参考电压(VREFH和VREFL)以及用于编程该缓冲器的二进制输入代码的十进制值确定。使用方程式(1)计算该值:

参考电压的有效电压范围为:

BUF16820输出能够在典型的5μs内实现满量程电压输出变化,无需中间步骤。

输出锁存器

更新DAC寄存器与更新DAC输出电压不同,因为BUF16820具有双缓冲寄存器结构。有三种方法可以将传输的数据从存储寄存器锁存到DAC中,以更新DAC输出电压。

方法1:需要在外部设置闩锁引脚(LD)LOW,LD=LOW,每当其对应的寄存器更新时,它就更新每个DAC输出电压。

方法2:在外部设置LD=HIGH,以允许所有DAC输出电压在数据传输期间保持其值,直到LD=LOW,然后同时将所有DAC的输出电压更新为新的寄存器值。使用此方法预先传输未来的数据集,以准备非常快速的输出电压更新。

方法3:采用软件控制。LD保持为高电平,当主设备在任何DAC寄存器的第15位写入“1”和在第14位写入“0”时,所有的DAC都会更新。更新发生在接收到当前写入寄存器的16位数据之后。

无论闩锁引脚的状态如何,通电后的一般呼叫重置或重置都会更新DAC。

OTP存储器的获取

通用的acquire命令将所有寄存器和DAC输出更新为存储在OTP存储器中的值。

单通道获取命令只更新与命令中使用的DAC地址对应的DAC的寄存器和DAC输出。

通用获取命令

1.在总线上发送启动条件。

2.发送设备地址,读/写位=低。BUF16820将确认该字节。

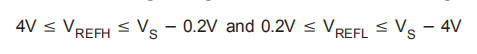

3.发送一个DAC地址字节。位D7−D5必须设置为100。位D4−D0是任何有效的DAC地址。只有地址00000到01101、10010、10011和10100是有效的,并且将被确认。表3显示了DAC地址。

4.在公共汽车上发送停车条件。

执行此命令后,所有的DAC寄存器和DAC输出都将更改为OTP内存值。

单通道采集命令

1.在总线上发送启动条件。

2.发送设备地址,读/写位=低。BUF16820将确认该字节。

3.使用与DAC输出相对应的DAC地址发送一个DAC地址字节,并用OTP内存值更新寄存器。位D7−D5必须设置为010。位D4−D0表示地址。只有地址00000到01101、10010、10011和10100是有效的,并且将被确认。表3显示了DAC地址。

4.在公共汽车上发送停车条件。

有关时序图,请参见图12。

读/写操作

单个或多个读写操作可以在单个通信事务中完成。写入DAC寄存器与写入OTP内存不同。数据最高有效字节的位D15−D14确定数据将被写入DAC寄存器还是OTP存储器。

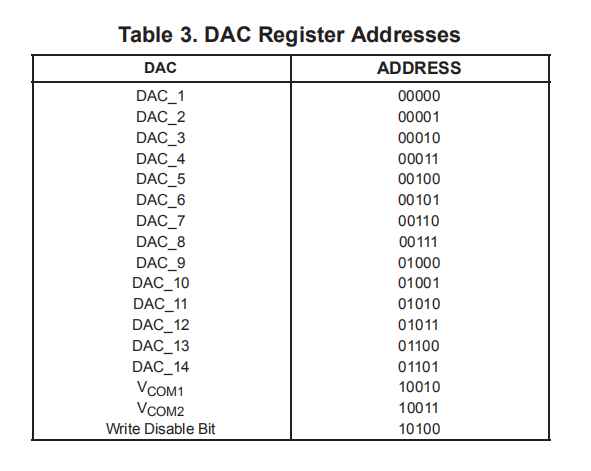

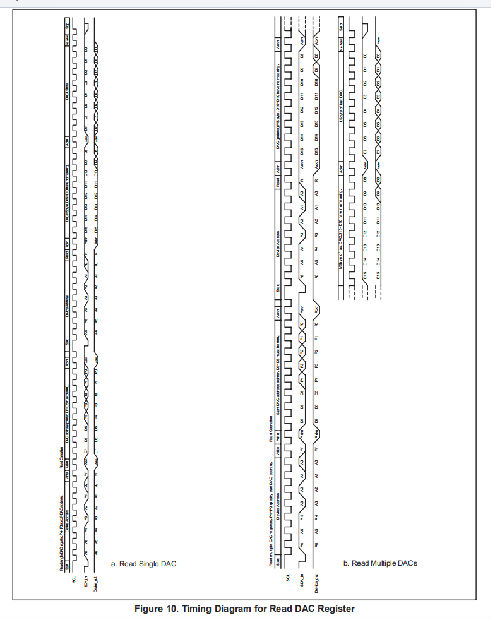

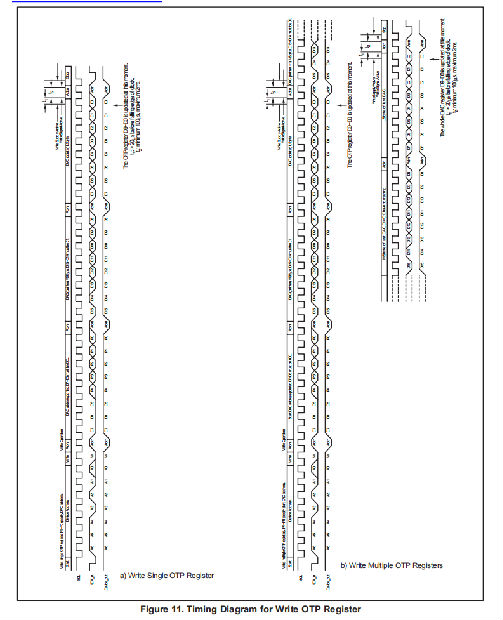

有关读/写命令的时序图和要求,请参见图9到图11。

读/写:DAC寄存器

BUF16820能够在单个通信中从单个DAC或多个DAC读取,或写入单个DAC或多个DAC的寄存器事务处理.DAC地址以00000开头(对应于DAC_1),一直到01101(对应于DAC_14)。地址10010和10011分别对应于VCOM1和VCOM2。地址10100对应于写禁用位。

通过将读/写位设置为低位来执行写入命令。将读/写位设置为高位执行读事务。

写作:

写入单个DAC寄存器:

1.在总线上发送启动条件。

2.发送设备地址,读/写位=低。BUF16820将确认该字节。

3.发送DAC或写禁用位地址字节。位D7−D5必须设置为0。位D4−D0表示地址。只有地址00000到01101、10010、10011和10100是有效的,并且将被确认。表3显示了DAC地址。

4.为指定的寄存器发送两个字节的数据。首先发送最高有效字节(位D15−D8,其中仅使用位D9和D8,且位D15−D14不得为01),然后发送最低有效字节(位D7−D0)。对于地址10100,只有D0有意义。该位是写禁用位。寄存器在接收到第二个字节后被更新。

5.在公共汽车上发送停车条件。

BUF16820确认每个数据字节。如果主机通过在总线上发送停止或启动条件而提前终止通信,则指定的寄存器将不会被更新。更新DAC寄存器与更新DAC输出电压不同;请参阅输出锁存部分。

更新多个DAC寄存器的过程与更新单个寄存器的过程相同。然而,在写入寻址寄存器后,主机不再发送停止条件,而是继续为下一个寄存器发送数据。在发送附加数据时,BUF16820会自动并按顺序逐步执行后续寄存器。该过程将继续,直到所有需要的寄存器都已更新或发出停止条件。

要写入多个DAC寄存器:

1.在总线上发送启动条件。

2.发送设备地址,读/写位=低。BUF16820将确认该字节。

3.发送从第一个DAC开始的DAC_1地址字节,或发送要更新的DAC序列中第一个DAC的地址字节。BUF16820将从该DAC开始,并按顺序逐步执行后续的DAC。

4.发送数据字节。首先发送最高有效字节(位D15−D8,其中只有位D9和D8有意义,并且位D15−D14不得为01),然后发送最低有效字节(位D7−D0)。前两个字节用于步骤3中寻址的DAC。它的寄存器在接收到第二个字节后自动更新。接下来的两个字节用于以下DAC;该DAC寄存器在接收到第四个字节后更新。此过程将继续,直到以下所有DAC的寄存器都已更新。BUF16820将继续接受总共20个DAC的数据;但是,第14个数据集之后的四个数据集将毫无意义。第19和第20组数据将适用于VCOM1和VCOM2。无法使用此方法访问写禁用位。必须使用写入单个DAC寄存器过程将其写入。

5.在公共汽车上发送停车条件。

BUF16820确认每个字节。要终止通信,请在总线上发送停止或启动条件。只有接收到两个字节数据的DAC寄存器才会被更新。

阅读:

读取DAC寄存器返回存储在DAC中的数据。此数据可能与存储在DAC寄存器中的数据不同;请参阅输出锁存器部分。

要读取DAC值:

1.在总线上发送启动条件。

2.发送设备地址,读/写位=低。BUF16820将确认该字节。

3.发送DAC地址字节。位D7−D5必须设置为0;位D4−D0是DAC地址。只有地址00000到01101、10010、10011和10100是有效的,并且将被确认。对于地址10100,只有D0有意义。该位是写禁用位。

4.发送启动或停止/启动条件。

5.发送正确的设备地址,读/写位=高。BUF16820将确认该字节。

6.接收两个字节的数据。它们用于指定的DAC。第一个接收到的字节是最高有效字节(位D15−D8;只有位D9和D8有意义),下一个字节是最低有效字节(位D7−D0)。

7.收到第一个字节后确认。

8.在总线上发送停止条件或不确认第二个字节以结束读取事务。

可通过在总线上发送过早停止或启动条件或不发送确认来终止通信。

要读取多个DAC:

1.在总线上发送启动条件。

2.发送设备地址,读/写位=低。BUF16820将确认该字节。

3.发送从第一个DAC开始的DAC_1地址字节,或发送要读取的DAC序列中第一个DAC的地址字节。BUF16820将从该DAC开始,并按顺序逐步执行后续的DAC。BUF16820将继续接受总共20个DAC的数据;但是,第14个数据集之后的四个数据集将毫无意义。第19和第20组数据将适用于VCOM1和VCOM2。

4.在总线上发送启动或停止/启动条件。

5.发送正确的设备地址,读/写位=高。BUF16820将确认该字节。

6.接收两个字节的数据。它们用于指定的DAC。第一个接收到的字节是最高有效字节(位D15−D8;只有位D9和D8有意义),下一个字节是最低有效字节(位D7−D0)。

7.接收到每个字节后确认。

8.当所有需要的DAC都被读取后,在总线上发送一个停止或启动条件。

可通过在总线上发送过早停止或启动条件或不发送确认来终止通信。

写入:用于DAC寄存器的OTP内存

BUF16820能够在单个通信事务中写入单个DAC或多个DAC的OTP内存。DAC地址以00000(对应于DAC_1)到01101(对应于DAC_14)开头。地址10010和10011对应于分别是VCOM1和VCOM2。地址10100对应于写禁用位。

对OTP存储器编程时,模拟电源电压必须在8.5V和18V之间。

通过将读/写位设置为低位来执行写入命令。

写入单个OTP寄存器:

1.在总线上发送启动条件。

2.发送设备地址,读/写位=低。BUF16820将确认该字节。

3.发送DAC地址字节。位D7−D5必须设置为0。位D4−D0是DAC地址。只有地址00000到01101、10010、10011和10100是有效的,并且将被确认。表3显示了DAC地址。

4.为指定DAC的OTP寄存器发送两个字节的数据。首先发送最高有效字节(位D15−D8,其中只有位D9和D8是数据位,位D15−D14必须是01),然后是最低有效字节(位D7−D0)。对于地址10100,只有D0有意义。该位是写禁用位。寄存器在接收到第二个字节后被更新。

5.在公共汽车上发送停车条件。

BUF16820将确认每个数据字节。如果主机通过在总线上发送停止或启动条件而提前终止通信,则指定的OTP寄存器将不会更新。写入OTP寄存器也会更新DAC寄存器和输出电压。

写入多个OTP寄存器:

1.在总线上发送启动条件。

2.发送设备地址,读/写位=低。BUF16820将确认该字节。

3.发送从第一个DAC的OTP寄存器开始的DAC_1地址字节,或发送要更新序列中第一个DAC的地址字节。BUF16820将从该DAC的OTP寄存器开始,并按顺序逐步执行后续寄存器。

4.发送数据字节。D0的有效位必须是D0的最低位(D0的有效位必须是D0的最低有效位,D8后面必须是d1的最低位)。前两个字节用于在步骤3中寻址的DAC的OTP寄存器。这个OTP寄存器在接收到第二个字节后自动更新。接下来的两个字节用于以下DAC的OTP寄存器(位D15−D14必须再次为01)。该DAC OTP寄存器在接收到第四个字节后被更新。此过程将继续,直到以下所有DAC OTP寄存器的寄存器都已更新。BUF16820将继续接受总共20个DAC的数据;但是,第14个数据集之后的四个数据集将毫无意义。第19和第20组数据将适用于VCOM1和VCOM2。无法使用此方法访问写禁用位。必须使用写入单个OTP寄存器过程将其写入。

5.在公共汽车上发送停车条件。

BUF16820将确认每个字节。要终止通信,请在总线上发送停止或启动条件。只有接收到两个字节数据的DAC寄存器才被编程。

OTP写入禁用

在寄存器10100的位D0中写入“1”将禁用将来的所有写入操作。这个位的状态可以像任何其他数据位一样被访问。在对OTP寄存器进行编程后,必须将该位设置为“1”,以防止对OTP寄存器的意外更改。在寄存器10100的位D0设置为“1”之前,任何OTP寄存器位都可以从“0”更改为“1”;但是,一旦将某个位设置为“1”,则不能将其设置回“0”。

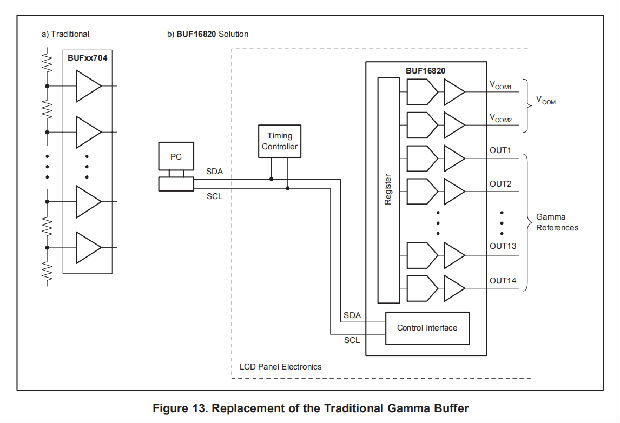

取代传统的伽马缓冲器

传统的gamma缓冲器依靠电阻串(通常使用昂贵的0.1%电阻)来设置伽马电压。在开发过程中,优化这些伽马电压可能很耗时。用BUF16820编程这些伽马电压可以显著减少伽马电压优化所需的时间。最终的gamma值可以写入内部OTP存储器,以取代传统的gamma缓冲解决方案。图13a显示了传统的电阻串;图13b显示了使用BUF16820的更有效的替代方法。

BUF16820采用当今最先进的高压CMOS工艺,这使得它能够与传统的伽马缓冲器相竞争。

可编程性具有以下优点:

*大大缩短了开发时间。

*通过消除18个以上的外部组件提高可靠性。

*消除面板之间的制造差异。

*允许客户在最终生产过程中使用多个伽马曲线来构建客户相关曲线。这种方法大大降低了库存成本和风险,简化了库存管理。

*只需上传一组不同的伽马值,就可以向液晶显示器制造商演示各种伽马曲线。

*允许在生产过程中对伽马曲线进行简单调整,以适应面板制造工艺或最终客户要求的变化。

*降低成本和空间。

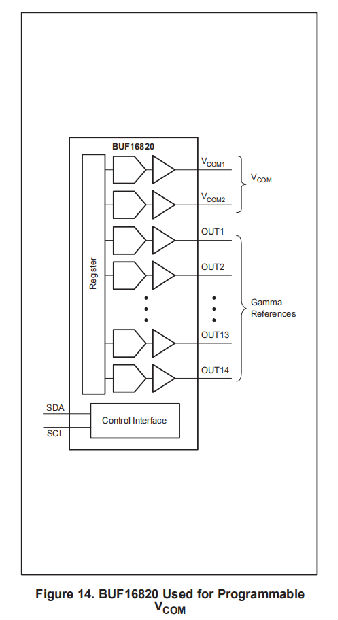

可编程VCOM

BUF16820的VCOM通道可以从正电源线切换到2.5V,而在输出电流为100mA时,可以从负电源线切换到1V(参见图4,典型的输出电压与输出电流的关系)。gamma和VCOM值可以永久存储在内部OTP存储器中。VCOM通道可独立于伽马通道编程。图14显示了用于VCOM电压的BUF16820。

REFH和REFL输入范围

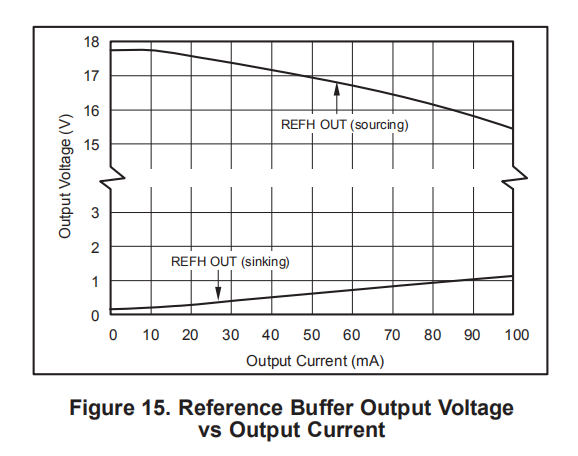

BUF16820的最佳性能和输出摆动范围是通过施加略低于电源电压的REFH和REFL电压实现的。大多数规格在REFH=VS−200mV和REFL=GND+200mV下进行了测试。这个REFH内部缓冲区的设计非常接近VS,REFL internal buffer被设计成与GND非常接近。然而,它们在饱和前摆动的距离是有限的。为避免内部REFH和REFL缓冲器饱和,REFH电压不得大于VS−100mV,REFL电压不得低于GND+100mV。图15显示了REFH和REFL缓冲区的摆动能力。

当试图最大化gamma缓冲器的输出摆动能力时,另一个考虑因素是输出缓冲器(OUT1−14、VCOM1和VCOM2)摆动范围的限制,这取决于负载电流。LCD应用中的典型负载是5mA到10mA。例如,如果OUT1的电源是10mA,则摆动通常限制在VS−200mV左右。这同样适用于OUT14,当下沉10mA时,它通常限制在GND+200mV。输出摆幅的增加只能在负载较轻的情况下实现。例如,3mA负载通常允许摆动增加到VS−100mV和GND+100mV左右。

将REFH直接连接到VS和REFL直接连接到GND不会损坏BUF16820。但是,如上所述,REFH和REFL缓冲器的输出级将饱和。这种情况并不理想,可能会导致测量的输出电压出现小误差输出1−14、VCOM1和VCOM2。如上所述,这种连接REFH和REFL的方法无助于最大化输出摆动能力。

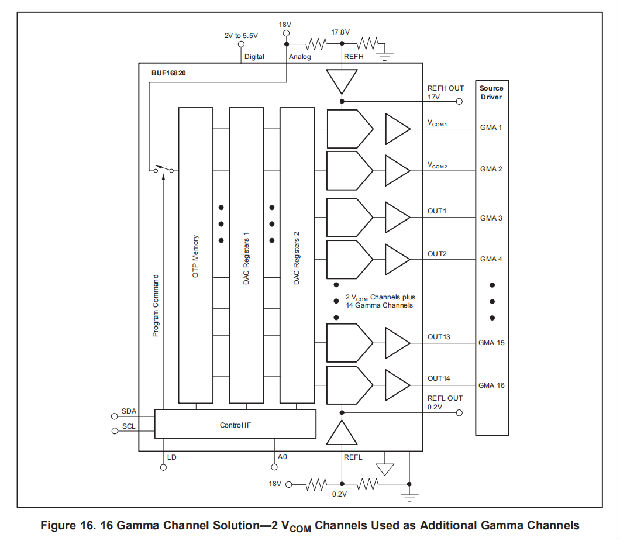

16个伽马通道的配置

VCOM输出可作为额外的伽马参考,以实现两个额外的伽马通道(总共16个)。当产生或吸收较小电流时,VCOM输出将与OUT1−9输出相同(参见典型特性,图4)。VCOM输出能够更好地摆动到正轨道,而不是反向轨道。因此,最好将VCOM输出用于更高的参考电压,如图16所示。

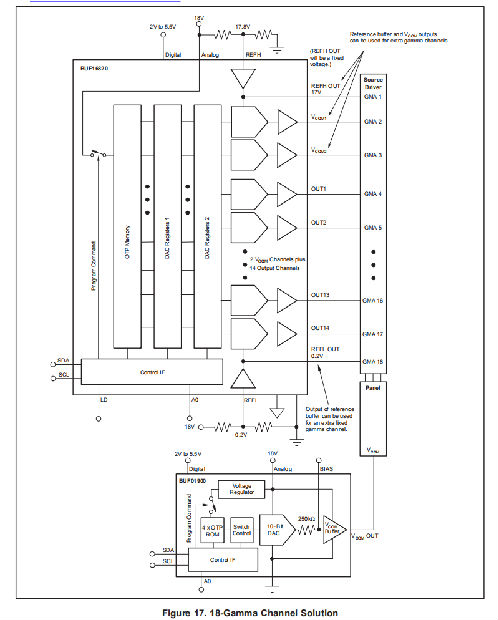

18个伽马通道的配置

除VCOM输出外,REFH和REFL OUT输出也可用作固定伽马参考。输出电压分别由REFH和REFL输入电压设置。因此,REFH OUT应用于最高电压gamma基准,REFL OUT用于最低电压gamma基准。通过使用所有14个输出、两个VCOM输出和两个REFH/L OUT输出,可以创建一个18通道的解决方案;见图17。然而,REFH和REFL OUT缓冲器设计为仅驱动5mA至10mA的轻负载。不建议使用这些缓冲器驱动电容性负载。此外,REFH和REFL缓冲器不得因REFH OUT或REFL OUT的源极/漏电流过大而饱和。REFH和REFL缓冲器的饱和导致OUT1−14的电压误差,VCOM1和VCOM2。BUF01900(预期于2006年第2季度发布)可用于提供可编程VCOM输出。

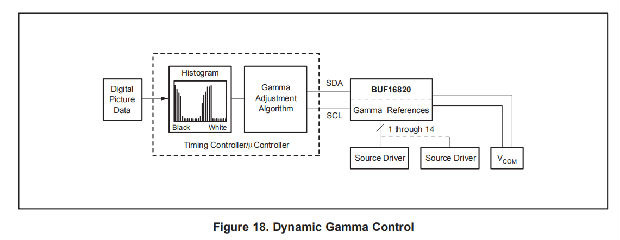

动态伽马控制

动态伽玛控制是一种用于改善液晶电视图像质量的技术。分析每个画面帧中的亮度,并逐帧调整伽马曲线。伽马曲线通常在视频信号中的短垂直消隐期间更新。图18显示了使用BUF16820进行动态伽马控制和VCOM输出的框图。

由于其独特的拓扑结构,BUF16820非常适合快速改变伽马曲线:

*DAC的双寄存器输入结构。

*快速串行接口。

*通过软件同步更新所有DAC。请参阅读/写操作和输出锁存器部分。

双寄存器输入结构通过允许将更新的DAC值预加载到第一寄存器组来节省编程时间。当图片仍在显示时,可以存储此数据。由于数据只存储在第一寄存器组中,所以DAC输出值保持不变,显示不受影响。在垂直同步期间,可以通过使用连接到LD管脚的附加控制线或通过软件在任何DAC寄存器的第15位写入“1”,来快速更新DAC输出(因此,伽马电压)。有关双寄存器输入结构操作的详细信息,请参阅输出锁存器部分。

例子:通过软件同时更新所有14个伽马寄存器。

第1步:检查LD引脚是否处于高状态。

第2步:写入DAC寄存器1−14,位15始终为“0”。

第3步:用相同的数据再次写入任何DAC寄存器。确保位15为“1”。所有的DAC通道将在接收到最后一位数据后同时更新。(注:此步骤可通过在上一步骤中将DAC 14的位15设置为“1”来消除。)

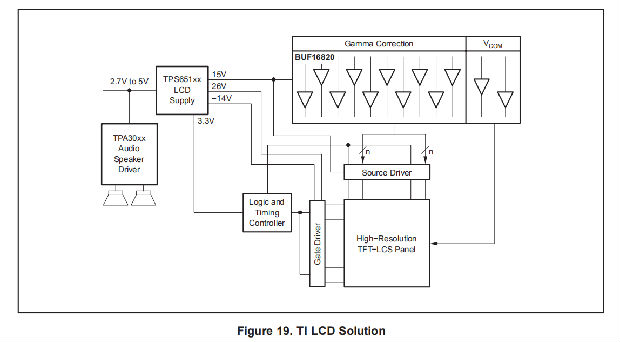

钛板整体解决方案

除了BUF16820可编程基准电压源外,TI还为LCD面板市场提供一整套集成电路,包括伽马校正缓冲器、各种电源解决方案和音频电源解决方案。TI的总IC溶液见图19。

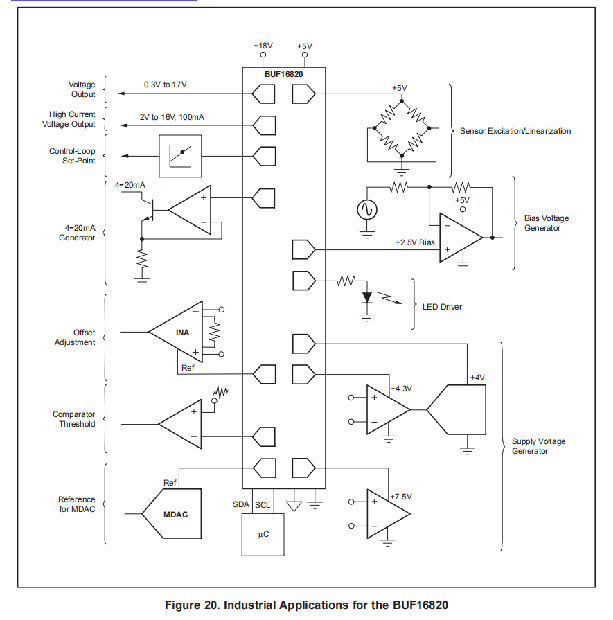

工业应用中的BUF16820

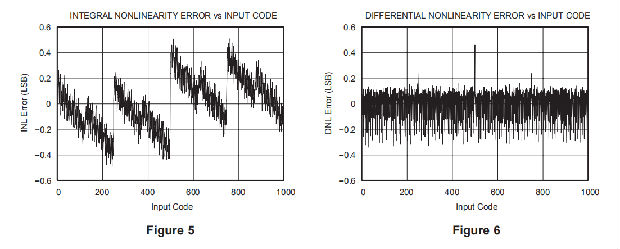

BUF16820电源范围广,输出电流高,成本极低,在可编程电源、多通道数据采集系统、数据记录器、传感器激励和线性化、电源生成等一系列中等精度工业应用中具有吸引力。每个DAC通道具有1LSB DNL和INL。

许多系统需要不同水平的偏压和电源,用于不同的部件,以及传感器励磁、控制回路设定点、电压输出、电流输出和其他功能。BUF16820有16个可编程DAC通道,通过允许设计者通过软件更改所有这些参数,为整个系统提供了极大的灵活性。

图20提供了在应用程序中如何使用BUF16820的各种示例。带有两线串行接口的微控制器控制BUF16820的各种DAC。BUF16820可用于:

*传感器激励

*可编程偏置/参考电压

*可变电源

*高电流电压输出

*4-20mA输出

*控制回路设定点发生器

注:通电时,BUF16820 DAC的输出电压设置为已编程的OTP存储器值,或者如果OTP值尚未编程,则设置为0000。

评估板和软件

BUF16820有一个评估委员会,如图21所示。评估板的特点是易于使用的软件,可以设置单独的通道电压。可以快速评估配置以确定给定应用程序的最佳代码。有关评估委员会的更多信息,请联系您当地的TI代表。

电源板设计的一般注意事项

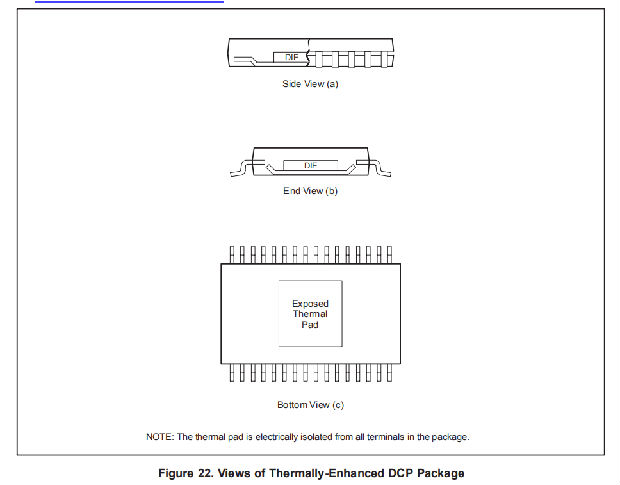

BUF16820提供热增强型PowerPAD封装。这个包装是用一个下装引线框架构造的,模具安装在上面;见图22(a)和图22(b)。这种布置导致引线框架暴露在封装底部的热垫上;见图22(c)。该热垫与模具直接热接触;因此,通过提供远离热垫的良好热路径,可获得优异的热性能。

PowerPAD包允许在一个制造操作中同时进行装配和热管理。在表面贴装焊料操作过程中(引线焊接时),必须将热焊盘焊接到封装下方的铜区域。通过在这个铜区域内使用热路径,热量可以从封装件传导到接地层或其他散热装置中。始终需要将PowerPAD焊接到印刷电路板(PCB),即使在低功耗的应用中也是如此。这在引线框架模架垫和PCB之间提供了必要的热连接和机械连接。

电源板必须连接到设备上最负的电源电压,即GNDA和GNDD。

1.准备带有顶部蚀刻图案的PCB。导线和热垫都应进行蚀刻。

2.在隔热垫区域放置推荐的孔。HTSSOP-32 DAP封装的理想热接地尺寸和热通孔模式(3x6)可在PowerPAD热增强封装(SLMA002)技术摘要中找到,可从以下网址下载:www.ti.com。这些孔的直径应为13密耳。保持它们很小,这样焊料芯吸通过孔在回流焊期间不是问题。

3.可在热垫区域外沿热平面的任何位置放置额外的通孔。这有助于消散BUF16820 IC产生的热量。这些额外的通孔可能比热垫正下方直径为13密耳的通孔大。它们可以更大,因为它们不在要焊接的热垫区域;因此,芯吸不是问题。

4.将所有孔连接到与GND引脚电压相同的内部平面。

5.将这些孔连接到内部平面时,不要使用典型的腹板或轮辐连接方法。网络连接有一个高热阻连接,有助于减缓焊接过程中的热传递。这使得具有平面连接的通孔的焊接更加容易。然而,在这种应用中,为了实现最有效的热传递,需要低热阻。因此,BUF16820 PowerPAD组件下的孔应与内部平面连接,并围绕电镀通孔的整个圆周进行完整连接。

6.顶部焊锡面罩应使封装端子和热垫区域露出10个孔。底部的焊接面罩应覆盖热焊盘区域的孔。这种掩蔽可以防止焊料在回流焊过程中被拉离热焊盘区域。

7.将锡膏涂在外露的热垫区域和所有IC端子上。

8.有了这些准备步骤,BUF16820集成电路被简单地放置在适当的位置,并作为任何标准的表面安装组件运行焊料回流焊操作。此准备工作可使零件正确安装。

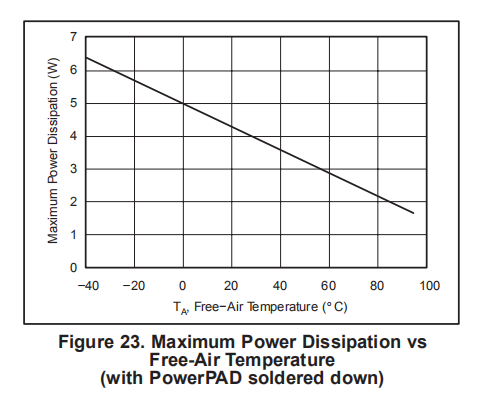

对于给定的θJA,最大功耗如图23所示,并通过等式3计算:

其中:

PD=最大功耗(W)

TMAX=绝对最高结温(+125°C)

TA=自由环境空气温度(°C)

θJA=θJC+θCA

θJC=从接头到外壳的热系数(°C/W)

θCA=从外壳到环境空气的热系数(°C/W)

安芯科创是一家国内芯片代理和国外品牌分销的综合服务商,公司提供芯片ic选型、蓝牙WIFI模组、进口芯片替换国产降成本等解决方案,可承接项目开发,以及元器件一站式采购服务,类型有运放芯片、电源芯片、MO芯片、蓝牙芯片、MCU芯片、二极管、三极管、电阻、电容、连接器、电感、继电器、晶振、蓝牙模组、WI模组及各类模组等电子元器件销售。(关于元器件价格请咨询在线客服黄经理:15382911663)

代理分销品牌有:ADI_亚德诺半导体/ALTBRA_阿尔特拉/BARROT_百瑞互联/BORN_伯恩半导体/BROADCHIP_广芯电子/COREBAI_芯佰微/DK_东科半导体/HDSC_华大半导体/holychip_芯圣/HUATECH_华泰/INFINEON_英飞凌/INTEL_英特尔/ISSI/LATTICE_莱迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_国民技术/NEXPERIA_安世半导体/NXP_恩智浦/Panasonic_松下电器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半导体/TD_TECHCODE美国泰德半导体/TI_德州仪器/VISHAY_威世/XILINX_赛灵思/芯唐微电子等等

免责声明:部分图文来源网络,文章内容仅供参考,不构成投资建议,若内容有误或涉及侵权可联系删除。

Copyright © 2002-2023 深圳市安芯科创科技有限公司 版权所有 备案号:粤ICP备2023092210号-1