特征

●最大转换时间20μs

●单+5V电源操作

●与16位ADS7813兼容

●易于使用的串行接口

●0.3“DIP-16和SO-16

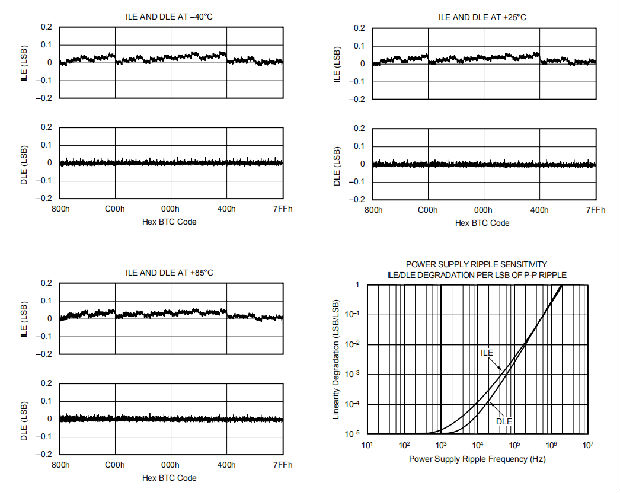

●±0.5LSB最大入口和DNL

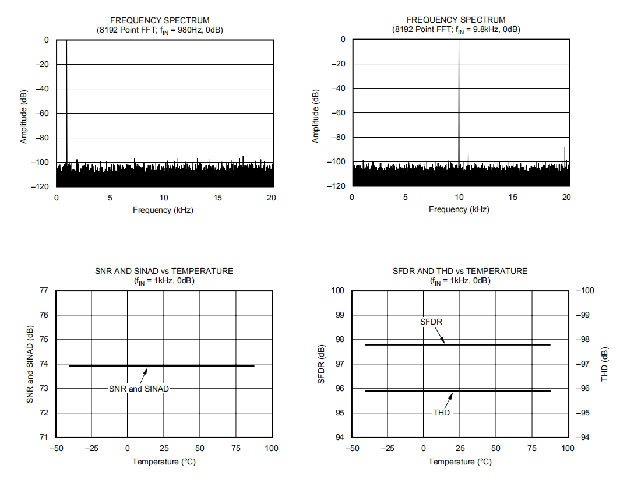

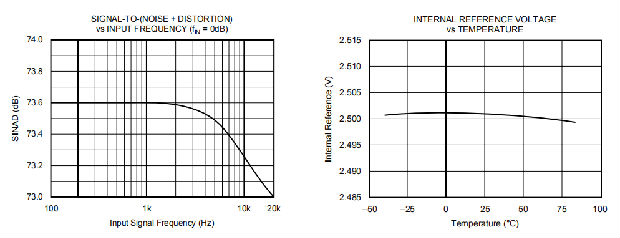

●最小信噪比72dB

●使用内部或外部参考

●多输入范围

●35mW最大功耗

●无缺失代码

●50μW断电模式

应用

●数据采集系统

●工业控制

●试验设备

●数字信号处理

说明

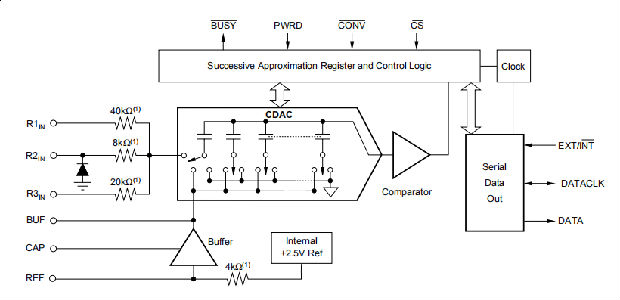

ADS7812是一款低功耗、单+5V电源、12位采样模数转换器。它包含一个完整的基于12位电容的SAR a/D,具有采样/保持、时钟、基准和串行数据接口。

转换器可配置为各种输入范围,包括±10V、±5V、0V至10V和0.5V至4.5V。还可提供高阻抗0.3V至2.8V输入范围(输入阻抗>10MΩ)。对于大多数输入范围,输入电压可以摆动到+16.5V或-16.5V,而不会损坏转换器。

灵活的SPI兼容串行接口允许数据与内部或外部时钟同步。ADS7812在-40°C至+85°C温度范围内以40kHz采样率指定。可提供0.3英寸DIP-16或SO-16封装。

注:(1)实际值可能变化±30%。

典型性能曲线

除非另有说明,否则在+5V输入下,+5V,=+5V输入。

基本操作

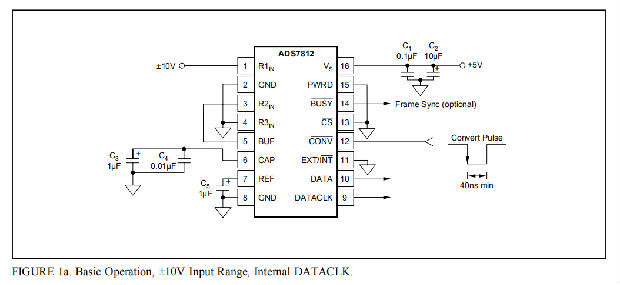

内部数据时钟

图1a显示了在±10V输入范围内操作ADS7812的基本电路。要开始转换并串行传输之前转换的结果,必须为CONV输入提供下降沿。“忙”将变低,表示转换已开始,并将保持低位,直到转换完成。在转换过程中,上一次转换的结果将通过数据传输,而DATACLK为串行数据提供同步时钟。MSB的12位是二进制的补码格式。每个数据位在数据时钟忙在整个串行传输过程中为低电平,可用作帧同步信号。

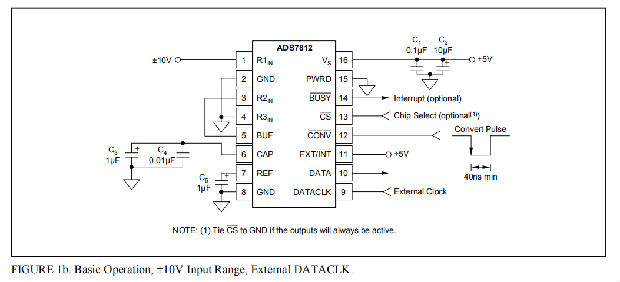

外部数据时钟

图1b显示了在±10V输入范围内操作ADS7812的基本电路。要开始转换,必须为CONV输入提供下降沿。“忙”将变低,表示转换已开始,并将保持低位,直到转换完成。就在转换接近结束时忙上升之前,保存转换结果的内部工作寄存器将被传输到内部移位寄存器。

内部移位寄存器通过DATACLK输入时钟。读取转换结果的推荐方法是在转换完成后提供串行时钟。有关详细信息,请参阅本数据表读取数据部分下的外部数据CLK。

开始转换

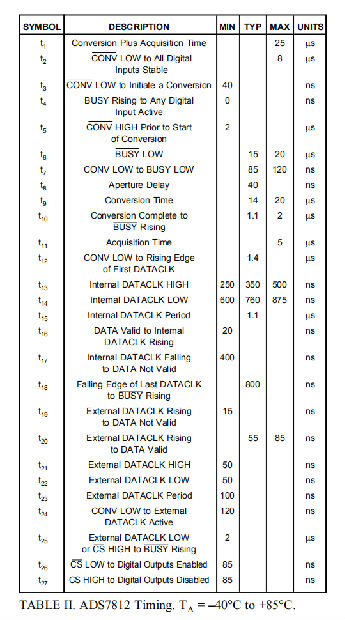

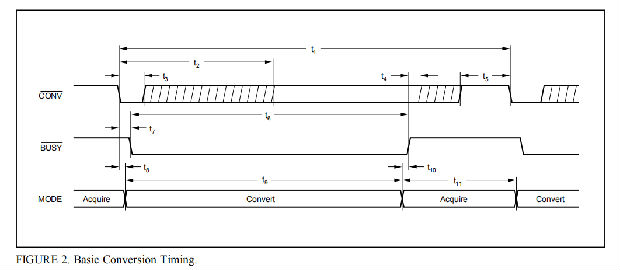

如果转换当前没有进行,CONV输入上的下降沿将样本和保持置于保持模式,并开始转换,如图2所示,时间如表II所示。在转换过程中,CONV输入被忽略。启动转换不依赖于CS的状态。每25μs(40kHz最大转换率)可启动一次转换。没有最低转换率。

即使在转换过程中忽略CONV输入,在转换期间该输入应保持静态。此数字输入上的转换可以很容易地耦合到转换器的敏感模拟部分,从而对转换结果产生不利影响(有关更多信息,请参阅本数据表的外部数字信号灵敏度部分)。

理想情况下,CONV输入应变低,并在整个转换过程中保持较低。它应该会在繁忙之后的某个时候回到高位。此外,在下一次转换开始之前,它应该是高的,在t5给出的最短时间段内。这将确保CONV输入上的数字转换不会影响为下一次转换而获取的信号。

可接受的替代方法是在转换开始后尽快返回CONV输入高电平。例如,一个100ns宽的负向脉冲可以产生一个良好的CONV输入信号。强烈建议从转换开始后的时间t2到BUSY上升,CONV输入应保持静态(高或低)。在此期间,转换器对外部噪声更为敏感。

读取数据

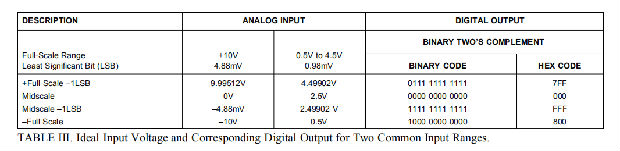

ADS7812的数字输出采用二进制二元复合(BTC)格式。表3显示了理想条件下数字输出字与模拟输入电压之间的关系。

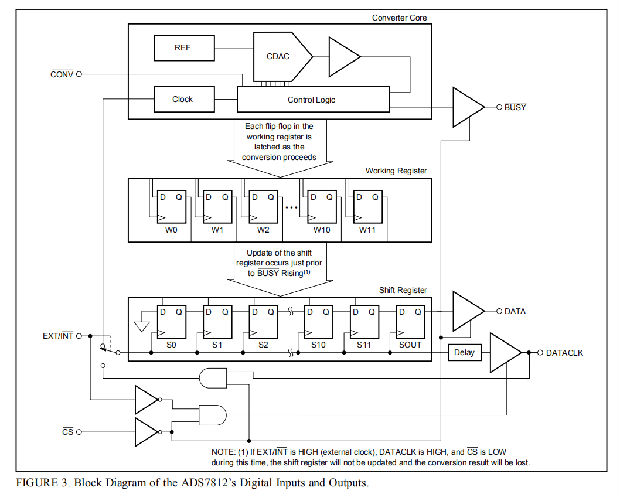

图3显示了ADS7812的各种数字输入、数字输出和内部逻辑之间的关系。

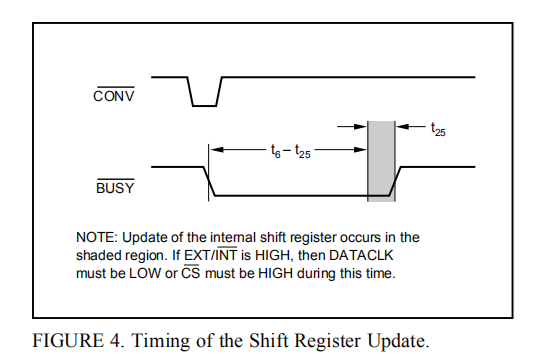

图4显示了何时更新ADS7812的内部移位寄存器,以及这与单个转换周期的关系。这两幅图共同指出了ADS7812的一个非常重要的方面:在转换完成之前,转换结果是不可用的。下面几节将讨论这一点的含义。

内部数据时钟

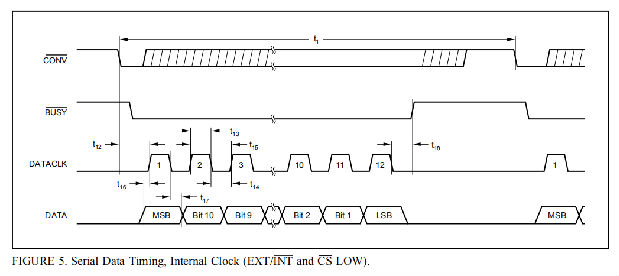

在EXT/INT连接低的情况下,转换“n”的结果在转换“n+1”期间串行传输,如图5所示,时间如表II所示。数据的串行传输仅在转换过程中发生。当传输未进行时,DATA和DATACLK低。

在转换过程中,先前转换的结果将通过数据传输,而DATACLK为串行数据提供同步时钟。数据格式为12位,二进制2的补码和MSB首先,每个人数据位在DATACLK的上升沿和下降沿都有效。在整个串行传输任务期间,忙碌度较低,可以用作帧同步信号。

外部数据时钟

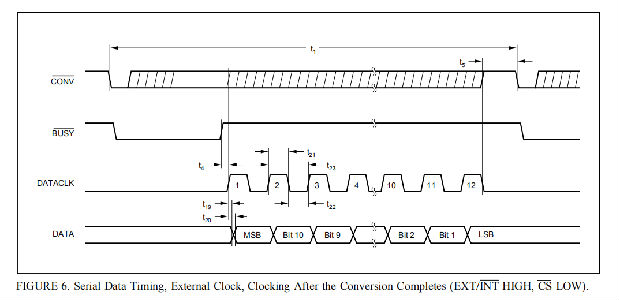

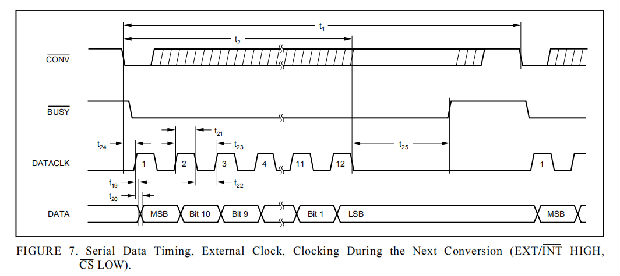

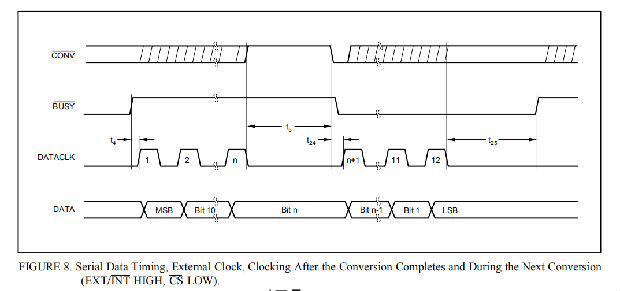

当EXT/INT处于高位时,转换“n”的结果在转换完成后、在下一个转换(“n+1”)期间或这两者的组合中计时。图6显示了转换完成后读取转换结果的情况。图7描述了在下一次转换期间读取结果的过程。图8结合了图6和图7的重要方面,即在转换完成后读取部分结果,在下一次转换期间读取其余部分。

转换结果的串行传输由DATACLK上的上升沿启动。MSB的12位是二进制的补码格式。每个数据位在DATACLK的下降沿有效。在某些情况下,可以使用DATACLK信号的上升沿。但是,最后一位需要一个额外的时钟周期(图6、7和8中没有显示)。

在繁忙上升之前,外部数据时钟信号必须为低或CS必须为高(参见图7和图8中的时间t25)。如果没有观察到这一点,ADS7812的输出移位寄存器将不会随着转换而更新结果。相反,则移位寄存器的先前内容将保留,新结果将丢失。

如果向DATACLK输入提供超过12个时钟周期,则数据输出将在第13个时钟周期的上升沿后变低。只要符合定时规范,ADS7812的操作就不会受到影响。在阅读下面三段之前,请查阅本数据的外部数字信号敏感度部分床单。这个将解释有关如何以及何时应用外部DATACLK信号的许多问题。

转换后激活外部数据时钟

获得转换结果的首选方法是在转换完成之后和下一次转换开始之前提供DATACLK信号,如图6所示。注意,在下一次转换开始之前,DATACLK信号应该是静态的。如果不提供,DATACLK信号可能会影响所采集的电压。

在下一次转换期间激活外部数据时钟

另一种获得转换结果的方法如图7所示。由于输出移位寄存器在转换结束之前不会更新,所以在下一次转换期间,上一个结果仍然有效。如果可以向ADS7812提供快速时钟(≥2MHz),则可以在时间t2期间读取结果。在此期间,来自DATACLK信号的噪声不太可能影响转换结果。

在转换后和下一次转换期间,外部数据时钟处于活动状态

图8显示了一个混合了前两种方法的方法。这种方法适用于一次进行8位串行传输的微控制器和速度较慢的微控制器。例如,如果微控制器能够产生的最快串行时钟为1μs,并且必须使用两个8位转换器来获取串行数据,则图6中所示的方法将导致吞吐量降低(26kHz最大转换率)。无法使用图7中描述的方法,因为将违反时间t25。图8中的方法提高了吞吐量(最大33kHz,时钟为1μs),并且DATACLK在t25期间较低。

与ADS7813的兼容性

ADS7812和ADS7813的唯一区别在于内部控制逻辑和数字接口。由于ADS7813是一个16位转换器,内部移位寄存器的宽度为16位。此外,在转换过程中只进行16位的决定。因此,ADS7813的转换时间约为ADS7812的133%。

本数据表中给出的时间安排将尽可能与ADS7813兼容。主要关注的是不同数量的串行时钟。如果设计必须同时兼容ADS7812和ADS7813,建议首先考虑ADS7813。如果该设计能与ADS7813配合使用,那么它肯定能与ADS7812配合使用。布局方面也是如此(参见本数据表的布局部分)。

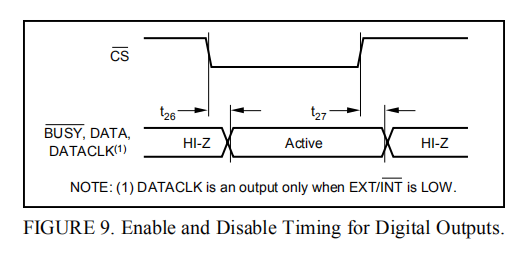

芯片选择(CS)

CS输入允许ADS7812的数字输出被禁用,并在EXT/INT高时对外部DATACLK信号进行选通。与CS相关的启用和禁用时间见图9,ADS7812的逻辑框图见图3。可随时禁用数字输出。

请注意,即使CS很高,转换也会在CONV的下降沿启动。如果在整个转换过程中EXT/INT输入低(内部DATACLK)而CS高,则先前的转换结果将丢失(串行传输发生,但DATA和DATACLK被禁用)。

模拟量输入

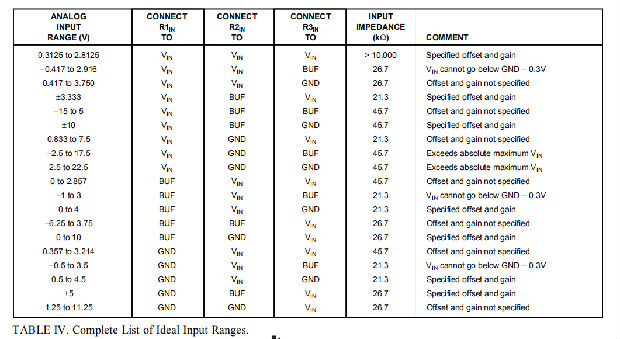

ADS7812提供多种输入范围。这是通过将三个输入电阻连接到模拟输入(VIN)、接地(GND)或2.5V参考缓冲器输出(BUF)来实现的。表一显示了数据采集应用中通常使用的输入范围。这些范围都是为了满足规格表中给出的规格而指定的。表四包含了理想输入范围、相关输入连接和有关范围的注释的完整列表。

输入阻抗来自各种连接和内部电阻值(参考本数据表首页的方框图)。内部电阻值为典型值,因工艺变化而变化±30%。然而,电阻的比率匹配要比这个好得多。因此,输入范围在各个部分之间只会变化十分之几个百分点,而输入阻抗的变化可能高达±30%。

规格表包含模拟输入范围变化的最大限制,但仅适用于注释字段显示指定偏移和增益的范围(包括表I中列出的所有范围)。对于其他范围,不测试偏移量和增益,也不指定。

表四中的五个输入范围不建议用于一般用途。对于其中两个,输入电压超过绝对最大值。只要输入电压保持在绝对最大值以下,这些范围仍然可以使用,但这将适度地显著降低转换器的满量程范围。

其他三个输入范围涉及在R2IN处的连接,该连接在地电位-0.3V以下驱动。该输入有一个反向的ESD保护二极管接地。如果R2IN接地以下,该二极管将正向偏置,并将根据温度将负输入钳制在-0.4V到-0.7V之间。在这里,这些范围仍然可以使用的成本的全刻度范围的转换器。

注意,表IV假设REF引脚处的电压为2.5V。如果使用内部参考电压或外部参考电压为2.5V,则这一点是正确的。其他参考电压将改变表IV中的值。

高阻抗模式

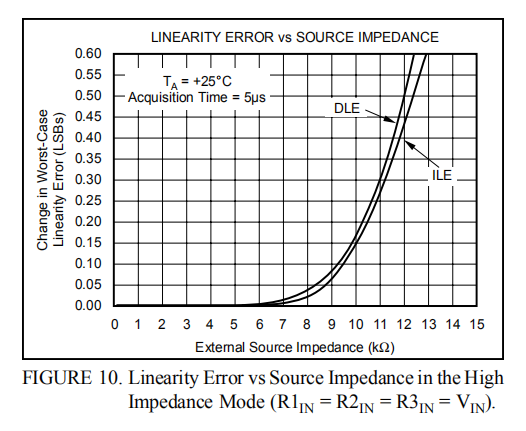

当R1IN、R2IN和R3IN连接到模拟输入时,ADS7812的输入范围为0.3125V至2.8125V,输入阻抗大于10MΩ。此输入范围可用于将ADS7812直接连接到各种传感器。图10显示了传感器的阻抗与ADS7812的ILE和DLE的变化。ADS7812的性能可以通过允许更多的采集时间来提高传感器阻抗。例如,对于相同的ILE/DLE性能,10μs的采集时间大约是传感器阻抗的两倍。

ADS7812的输入阻抗和电容随温度变化非常稳定。假设传感器也是如此,在ADS7812的指定温度范围内,图10所示的图形变化将小于百分之几。如果传感器阻抗随温度变化很大,则应使用最坏情况下的阻抗。

驱动ADS7812模拟输入

一般来说,任何“相当快”、高质量的运算或仪表放大器都可以用来驱动ADS7812输入。当转换器进入采集模式时,从转换器的输入到放大器的输出有一些电荷注入。这会导致较慢放大器的稳定时间不足。使用单电源放大器时要非常小心,尤其是当它们的输出需要摆得非常靠近电源轨时。

此外,注意放大器的线性度。单电源和“轨对轨”放大器的输出在接近电源轨时可能饱和。而不是放大器的传递函数是一条直线,曲线可以变成严重的“s”形。另外,注意放大器从源电流切换到反相电流的点。对于某些放大器,传递函数在这一点上可能明显不连续,导致输出电压的显著变化,而输入电压的变化要小得多。

德州仪器制造各种各样的操作和仪表放大器,可用于驱动ADS7812的输入。其中包括OPA627、OPA134、OPA132和INA110。

参考文献

ADS7812可以使用其内部2.5V参考电压或外部参考电压进行操作。通过向REF引脚施加外部参考电压,内部参考电压被过度驱动。REF输入端的电压由单位增益缓冲器进行内部缓冲。缓冲器的输出出现在BUF和CAP引脚上。

REF

REF引脚是内部2.5V参考的输出或外部参考的输入。1μF至2.2μF钽电容器应连接在该引脚和接地之间。电容器应尽可能靠近ADS7812。

当使用内部基准时,参考销不应连接到任何类型的有效负载上。外部负载将导致与内部参考串联的内部4kΩ电阻器之间的电压降。即使接地的4MΩ外部负载也会导致转换器的满标度范围降低4 LSB。

参考电压范围是参考电压2的全量程。增加参考电压将增加相对于内部噪声源的LSB大小,这反过来又可以提高信号的音调噪声比。同样,降低参考电压将减小LSB大小和信噪比。

CAP

盖销用于补偿内部参考缓冲器。应将1μF钽电容器与0.01μF陶瓷电容器并联,并将陶瓷电容器放置在尽可能靠近ADS7812的位置。端盖管脚上的电容值对ADS7812的最佳性能至关重要。大于2.0μF的值可能会过度补偿缓冲区,而低于0.5μF的值可能无法提供足够的补偿。

缓冲器

BUF引脚上的电压是内部参考缓冲器的输出。该引脚用于向模拟输入或各种输入提供+2.5V配置BUF输出可以为外部负载提供高达1mA的电流。负载应该是恒定的,因为可变负载会通过调制BUF电压来影响转换结果。还请注意,当在转换。介于转换后,BUF输出是安静的。

断电

ADS7812有一个断电模式,通过将CONV设置为低,然后将PWRD设为高。这将关闭包括参考电路在内的所有模拟电路的电源,将功耗降低到50μW以下。要退出断电模式,CONV取高,然后PWRD取低。注意,如果PWRD取高而CONV低,则转换将启动。

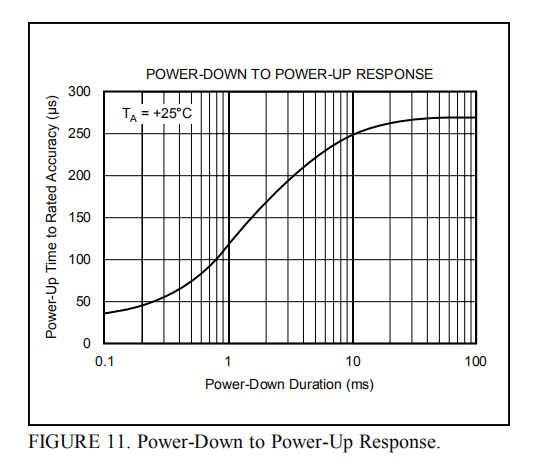

在断电模式下,连接到CAP和REF的电容器上的电压将开始泄漏。电容器电容器上的电压漏失比REF电容器快得多(当PWDN很高时,ADS7812的REF输入变得高阻抗,这对于电容器输入是不正确的)。当退出掉电模式时,必须允许这些电容器重新充电并稳定到12位电平。图11显示了根据断电所花费的时间(在室温下),获得有效的12位结果通常需要的时间量。该图假设盖脚上的总电容为1.01μF。

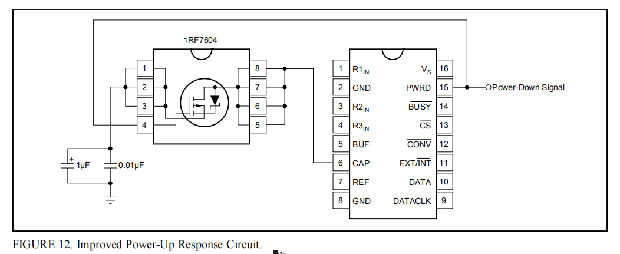

图12提供了一个电路,如果断电时间相当短(几秒钟或更少),则可以显著缩短通电时间。低导通电阻MOSFET用于断开盖引脚上的电容与ADS7812内部的泄漏路径。这使得电容器能够在更长的时间内保持充电,从而减少了通电时充电所需的时间。有了这个电路,断电时间可以延长到几十或几百毫秒,几乎是瞬间通电。

布局

ADS7812应被视为精密模拟元件,并应完全位于印刷电路板的“模拟”部分。理想情况下,接地层应延伸至ADS7812下方和所有其他模拟元件下方。该平面应与数字地面分开,直到它们在电源连接处连接。这将有助于防止动态数字接地电流通过电源接地的公共阻抗。

对于设计。一可能是从位于ADS7812附近的线性调节器获得+5V电源。如果源于数字+5V电源,5Ω至10Ω电阻器应与数字电源的电源连接串联。可能还需要增加VS引脚附近的旁路电容(与10μF和0.1μF电容器并联的额外100μF或更大电容器)。对于具有大量数字元件或非常高速数字逻辑的设计,这种简单的电源滤波方案可能不够。

对外部数字信号的灵敏度

所有基于逐次逼近寄存器的A/D转换器都对外部噪声源敏感。其原因将在以下段落中解释。对于ADS7812和类似的A/D转换器,这种噪声通常是由外部数字信号的转换引起的。虽然运行在转换器附近的数字信号可能是噪声源,但最大的问题是转换器本身的数字输入。

在许多情况下,系统设计者可能没有意识到存在问题或潜在的问题。对于12位系统,这些问题通常发生在最低有效位,并且仅发生在转换器传递函数的某些位置。对于一个16位转换器,这个问题更容易发现。

例如,图2中的时序图显示,在时间t2期间,CONV信号应该返回高电平。事实上,在转换过程中,CONV信号可以随时返回高电平。然而,在时间t2之后,CONV信号的转换有可能在ADS7812芯片上产生大量噪声。如果这种转换恰好发生在错误的时间,转换结果可能会受到影响。以类似的方式,DATACLK输入上的转换可能会影响转换结果。

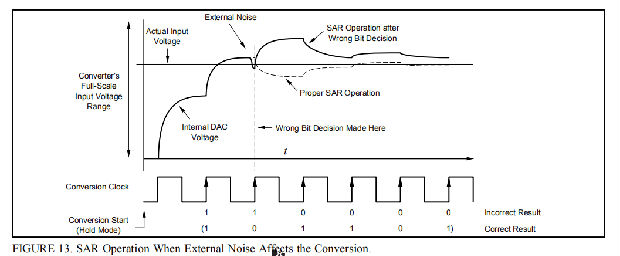

对于ADS7812,在转换过程中有12个独立的位决定。首先作出最高有效位的决定,在转换结束时进行到最低有效位。每一个位决策都涉及到被测位应该被设置的假设。这与迄今取得的成果相结合。转换器将这个综合结果与实际输入电压进行比较。如果合并结果太高,则清除该位。如果结果等于或低于实际输入电压,则位保持高位。这就是为什么基本架构被称为“逐次逼近寄存器”

如果到目前为止的结果是非常接近实际输入电压,那么比较涉及两个非常接近的电压。ADS7812的设计使得内部噪声源在比较器结果被锁存之前是最小的。但是,如果此时外部数字信号发生转换,大量噪声将耦合到ADS7812的敏感模拟部分。即使这种噪声只在两个电压之间产生2mV的差异,转换结果也将被3个计数或最低有效位(lsb)所关闭。(无论输入范围如何,ADS7812的内部LSB大小为610μV。)

一旦数字转换导致比较器做出错误的位决定,则无法纠正该决定。所有随后的比特判定都将是错误的(除非采用了某种类型的纠错)。图13显示了一个出错的逐次逼近过程。虚线表示正确的位决定应该是什么。实线表示转换的实际结果。

在最敏感的时间段里,最敏感的是时间。此外,由于大多数数字信号在少数情况下发生转换,所以由数字转换产生的噪声“事件”的峰值部分相当短暂纳秒随后的噪声可能会持续比这更长的时间,并可能导致进一步的影响,这需要更长的稳定时间;但是,通常情况下,事件在几十分钟内结束纳秒。

对于ADS7812,当第10位被决定时进行纠错。在该比特判定期间,可以纠正先前比特判定期间可能发生的有限错误。然而,在第10位之后,不可能进行这种校正。注意,对于图2、5、6、7和8中所示的时序图,所有外部数字信号应在转换开始后从8μs保持静态,直到繁忙上升。在转换过程中,第10位被确定为大约10μs到11μs。

应用程序信息

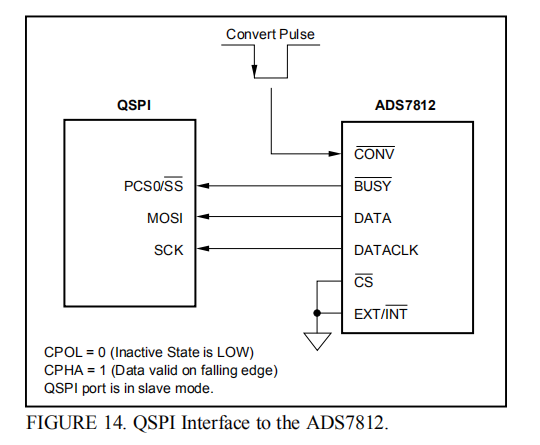

QSPI接口

图14显示了ADS7812和任何配备排队串行外围接口(QSPI)的微控制器(可在多个摩托罗拉设备上使用)之间的简单接口。此接口假定转换脉冲不是来自微控制器,并且ADS7812是唯一的串行外围设备。

在启用QSPI接口之前,微控制器必须配置为监控从选择(SS)线路。当发生从低到高的转换(指示转换结束)时,可以启用端口。如果不这样做,微控制器和A/D转换器可能无法正确同步。(从选择行仅启用通信,它不指示串行传输的开始或结束。)

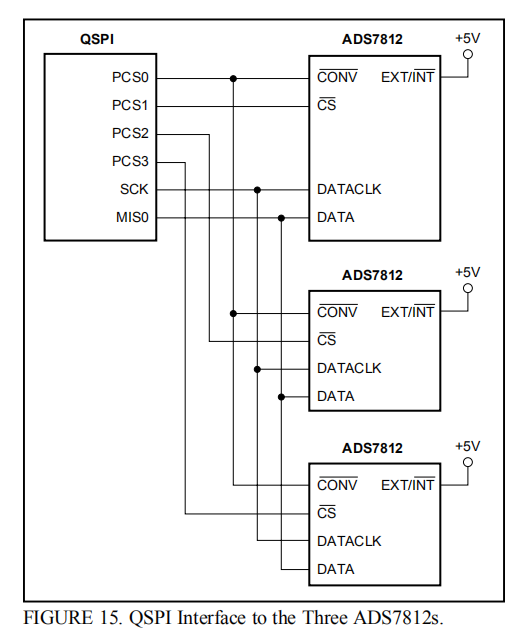

图15显示了一个安装了QSPI的微控制器接口,与三个ads7812相连。这种接口方案有许多可能的变化。如图所示,QSPI端口产生一个公共CONV信号,该信号在所有三个转换器上启动转换。转换完成后,依次传输每个结果。QSPI端口完全可编程,无需处理器干预即可处理定时和传输。如果以这种方式生成CONV信号,则可以使用ADS7812进行交流和直流测量,因为CONV信号的抖动很低。注意,如果CONV信号是通过软件命令生成的,它将有大量的抖动,并且只能进行低频(DC)测量。

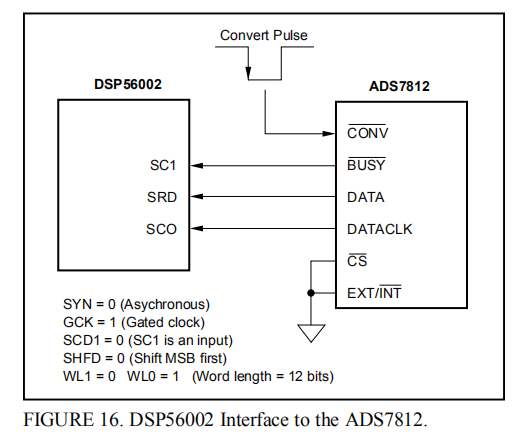

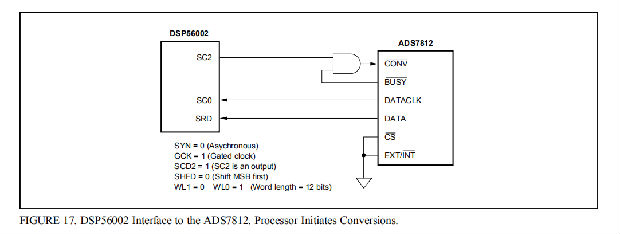

DSP56002接口

DSP56002串行接口具有串行外围接口(SPI)兼容性模式,并进行了一些增强。图16显示了ADS7812和DSP56002之间的接口。与图14中的QSPI接口一样,必须对DSP56002进行编程,以便在SCI上发生从低到高的转换时启用串行接口。

DSP56002还可以提供CONV信号,如图17所示。接口的接收和发送部分被解耦(异步模式),传输部分被设置为每隔一个传输帧生成一个字长帧同步(帧速率分配器设置为2)。预标度模数应设置为以所需转换率的两倍生成传输帧。

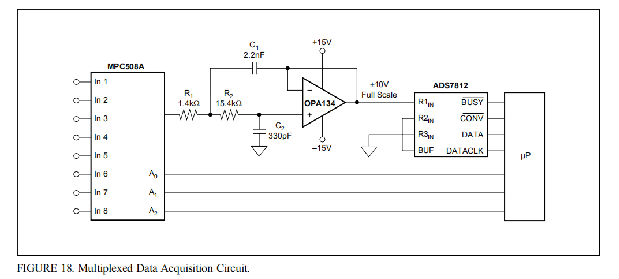

电路应用

图18显示了使用ADS7812的多路数据采集电路。MPC508A提供多路复用功能,而OPA134被配置为一个Sallen-Key,两极,单位增益低通滤波器。

安芯科创是一家国内芯片代理和国外品牌分销的综合服务商,公司提供芯片ic选型、蓝牙WIFI模组、进口芯片替换国产降成本等解决方案,可承接项目开发,以及元器件一站式采购服务,类型有运放芯片、电源芯片、MO芯片、蓝牙芯片、MCU芯片、二极管、三极管、电阻、电容、连接器、电感、继电器、晶振、蓝牙模组、WI模组及各类模组等电子元器件销售。(关于元器件价格请咨询在线客服黄经理:15382911663)

代理分销品牌有:ADI_亚德诺半导体/ALTBRA_阿尔特拉/BARROT_百瑞互联/BORN_伯恩半导体/BROADCHIP_广芯电子/COREBAI_芯佰微/DK_东科半导体/HDSC_华大半导体/holychip_芯圣/HUATECH_华泰/INFINEON_英飞凌/INTEL_英特尔/ISSI/LATTICE_莱迪思/maplesemi_美浦森/MICROCHIP_微芯/MS_瑞盟/NATION_国民技术/NEXPERIA_安世半导体/NXP_恩智浦/Panasonic_松下电器/RENESAS_瑞莎/SAMSUNG_三星/ST_意法半导体/TD_TECHCODE美国泰德半导体/TI_德州仪器/VISHAY_威世/XILINX_赛灵思/芯唐微电子等等

免责声明:部分图文来源网络,文章内容仅供参考,不构成投资建议,若内容有误或涉及侵权可联系删除。

Copyright © 2002-2023 深圳市安芯科创科技有限公司 版权所有 备案号:粤ICP备2023092210号-1